2021-10-03 18:53:57 索煒達(dá)電子 1022

項(xiàng)目編號(hào):E1360

文件大?。?.14M

源碼說(shuō)明:帶中文注釋

開(kāi)發(fā)環(huán)境:Verilog

簡(jiǎn)要概述:

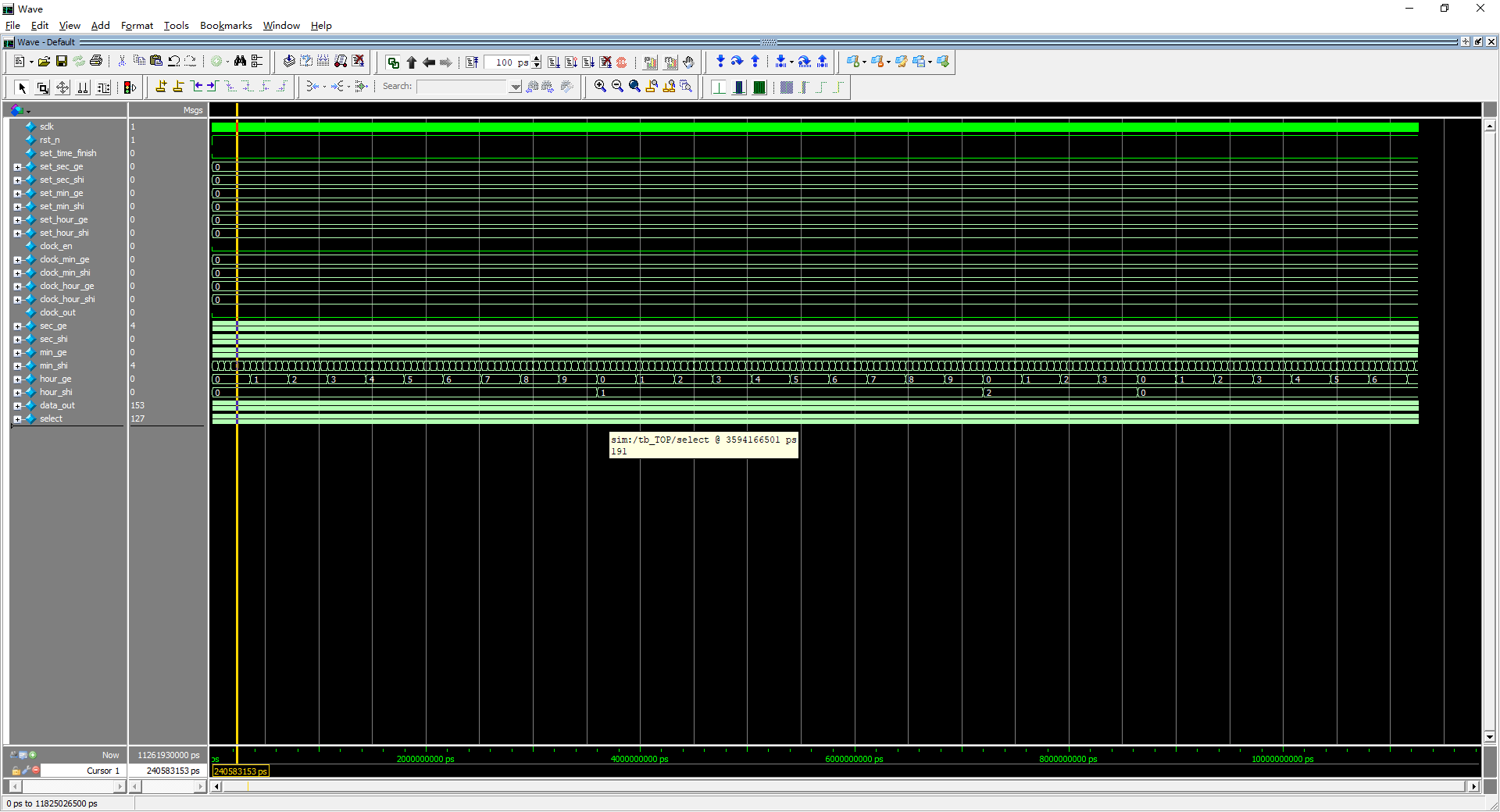

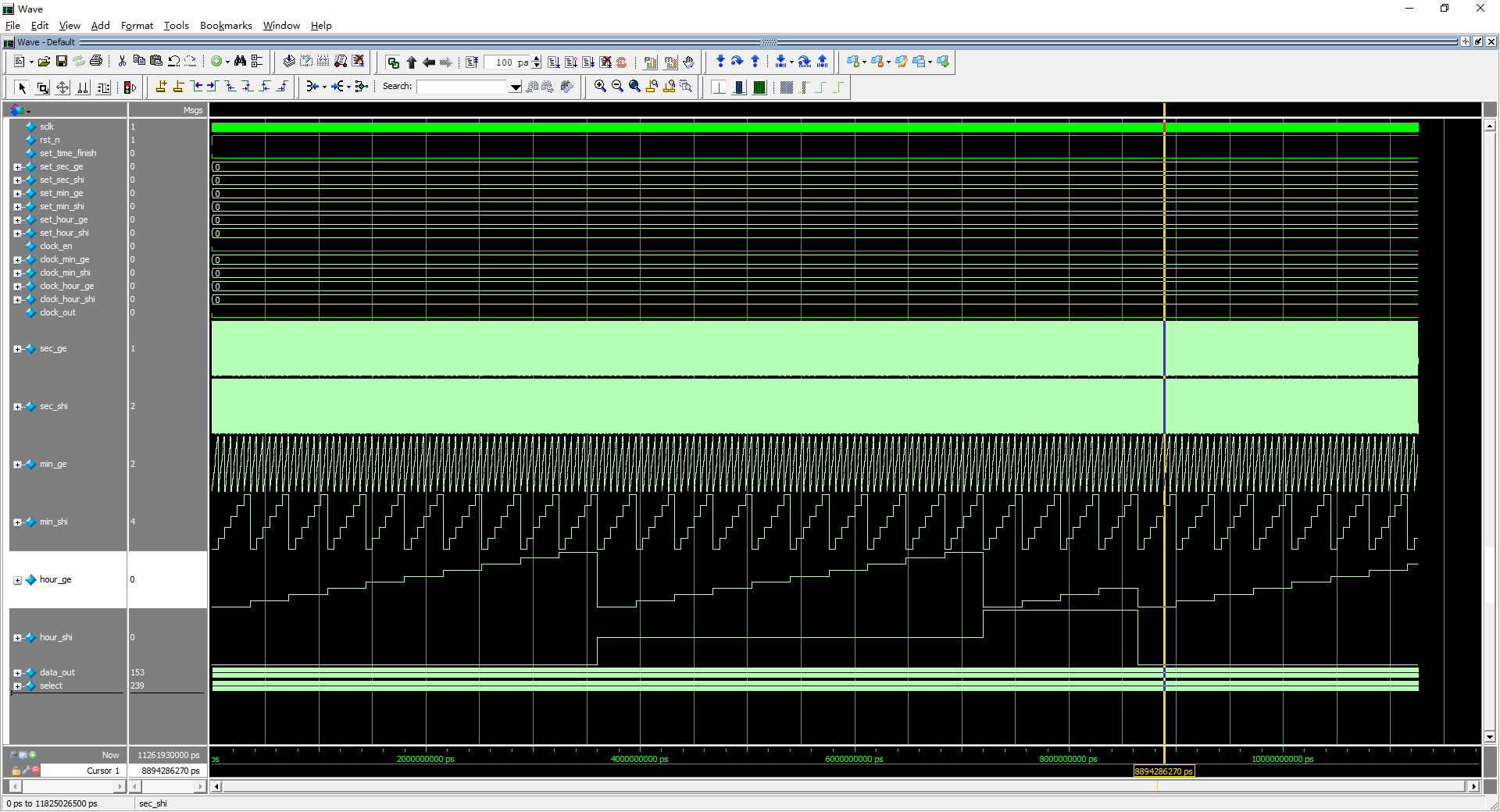

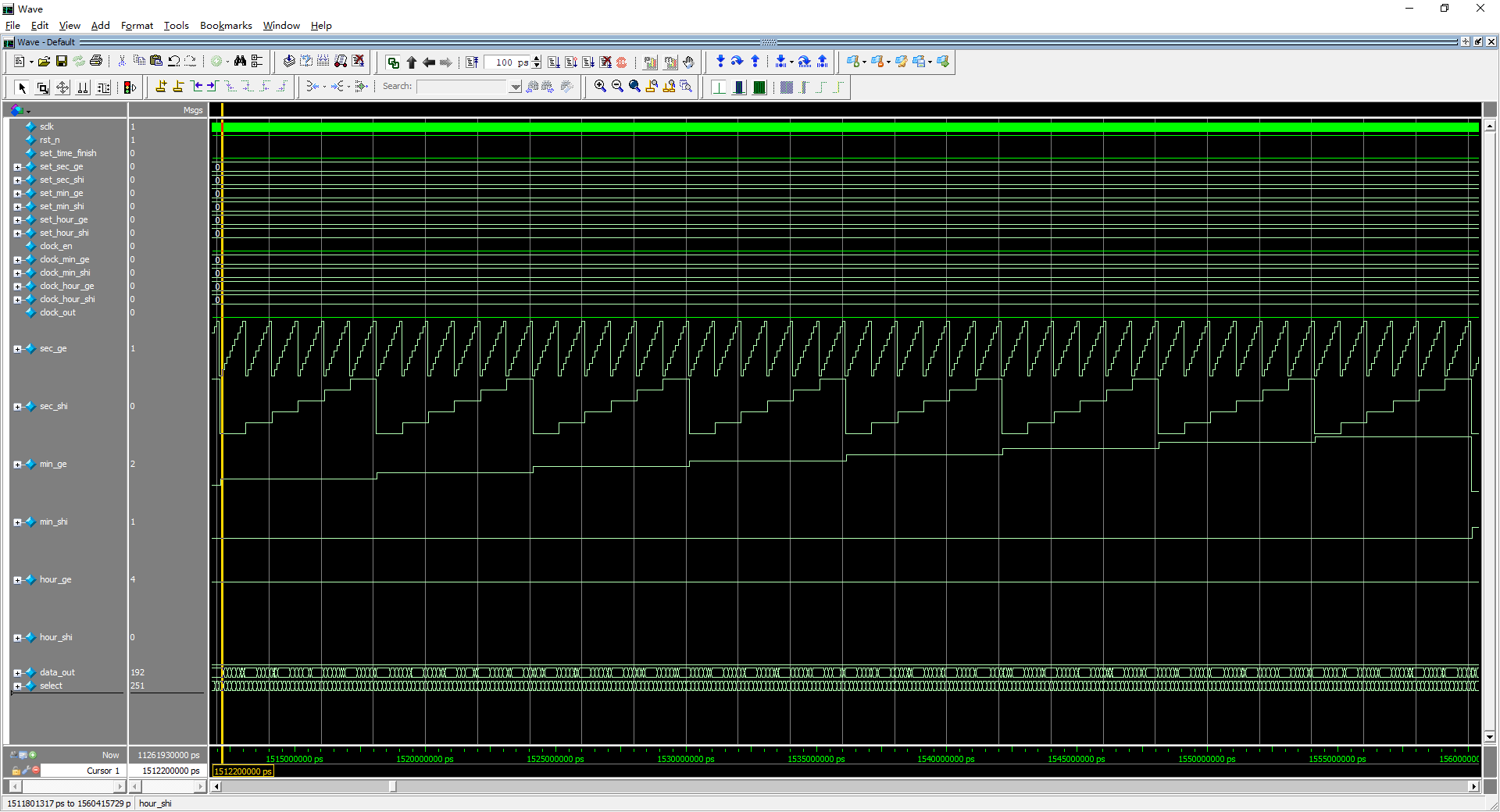

基于FPGA的數(shù)字時(shí)鐘(Modelsim仿真)

仿真圖

目錄│文件列表:

└ 基于FPGA的數(shù)字時(shí)鐘(Modelsim仿真)

└ Digital_Clock

│ Digital_Clock.qpf

│ Digital_Clock.qsf

│ Digital_Clock.qws

│ Digital_Clock_nativelink_simulation.rpt

│ RTL.png

│ 仿真圖1.png

│ 仿真圖2.png

│ 仿真圖3.png

├ Code

│ │ display_ctrl.v

│ │ time_control.v

│ └ TOP.v

├ db

│ │ Digital_Clock.(0).cnf.cdb

│ │ Digital_Clock.(0).cnf.hdb

│ │ Digital_Clock.(1).cnf.cdb

│ │ Digital_Clock.(1).cnf.hdb

│ │ Digital_Clock.(2).cnf.cdb

│ │ Digital_Clock.(2).cnf.hdb

│ │ Digital_Clock.ae.hdb

│ │ Digital_Clock.cbx.xml

│ │ Digital_Clock.cmp.rdb

│ │ Digital_Clock.db_info

│ │ Digital_Clock.hier_info

│ │ Digital_Clock.hif

│ │ Digital_Clock.lpc.html

│ │ Digital_Clock.lpc.rdb

│ │ Digital_Clock.lpc.txt

│ │ Digital_Clock.map.cdb

│ │ Digital_Clock.map.hdb

│ │ Digital_Clock.map.logdb

│ │ Digital_Clock.map.qmsg

│ │ Digital_Clock.map.rdb

│ │ Digital_Clock.npp.qmsg

│ │ Digital_Clock.pplq.rdb

│ │ Digital_Clock.pre_map.cdb

│ │ Digital_Clock.pre_map.hdb

│ │ Digital_Clock.root_partition.map.reg_db.cdb

│ │ Digital_Clock.rtlv.hdb

│ │ Digital_Clock.rtlv_sg.cdb

│ │ Digital_Clock.rtlv_sg_swap.cdb

│ │ Digital_Clock.sgate.nvd

│ │ Digital_Clock.sgate_sm.nvd

│ │ Digital_Clock.sld_design_entry.sci

│ │ Digital_Clock.sld_design_entry_dsc.sci

│ │ Digital_Clock.smart_action.txt

│ │ Digital_Clock.tis_db_list.ddb

│ └ prev_cmp_Digital_Clock.qmsg

├ incremental_db

│ │ README

│ └ compiled_partitions

│ │ Digital_Clock.db_info

│ └ Digital_Clock.root_partition.map.kpt

├ output_files

│ │ Digital_Clock.done

│ │ Digital_Clock.flow.rpt

│ │ Digital_Clock.map.rpt

│ └ Digital_Clock.map.summary

├ simulation

│ └ modelsim

│ │ Digital_Clock_run_msim_rtl_verilog.do

│ │ Digital_Clock_run_msim_rtl_verilog.do.bak

│ │ Digital_Clock_run_msim_rtl_verilog.do.bak1

│ │ Digital_Clock_run_msim_rtl_verilog.do.bak10

│ │ Digital_Clock_run_msim_rtl_verilog.do.bak11

│ │ Digital_Clock_run_msim_rtl_verilog.do.bak2

│ │ Digital_Clock_run_msim_rtl_verilog.do.bak3

│ │ Digital_Clock_run_msim_rtl_verilog.do.bak4

│ │ Digital_Clock_run_msim_rtl_verilog.do.bak5

│ │ Digital_Clock_run_msim_rtl_verilog.do.bak6

│ │ Digital_Clock_run_msim_rtl_verilog.do.bak7

│ │ Digital_Clock_run_msim_rtl_verilog.do.bak8

│ │ Digital_Clock_run_msim_rtl_verilog.do.bak9

│ │ modelsim.ini

│ │ msim_transcript

│ │ vish_stacktrace.vstf

│ │ vsim.wlf

│ └ rtl_work

│ │ _info

│ │ _lib.qdb

│ │ _lib1_0.qdb

│ │ _lib1_0.qpg

│ │ _lib1_0.qtl

│ └ _vmake

└ TestBench

└ tb_TOP.v